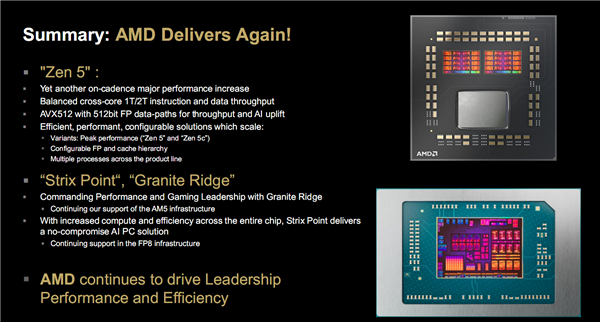

之前趁着参加AMD Zen5技术日活动,我们和大家分享过Zen5的架构设计特性,但和以往不同,当时公布的资料并不多,并未涉及到架构底层细节,也缺乏和Zen4的全面对比。

最近,AMD更新了Zen5架构技术文档,终于公布了我们想要的大量细节,包括各个微架构模块的具体变化,包括桌面端、移动端的异同,包括Zen5、Zen5c的新理念,包括同样升级的RDNA 3.5 GPU、XDNA 2 NPU。

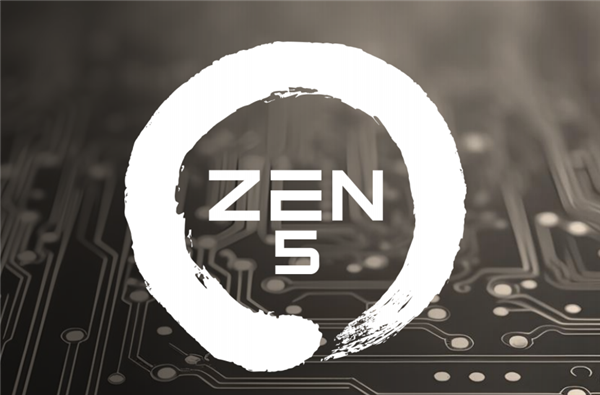

Zen5的目标就很简单,核心就是继续大幅提升单核、双核性能,为未来奠定新的基础,同时实现满血版AVX-512,支持可配置的256/512位浮点数据路径,有助于大大提升ai能力。

令人唏嘘的是,Intel 12代酷睿开始采用异构混合架构,其中E核不支持AVX-512,导致整体不得不放弃。

Zen5还有一个重要使命就是进一步普及紧凑版核心,也就是Zen5c,包括移动端和服务器端。

上一代其实就有了Zen4、Zen4c,并在数据中心端大放异彩,而在移动端只是非常低调地小试牛刀,这次要大面积普及。

不过AMD明确表示,Zen5c这种设计在桌面端不会使用,原因后边再讲。

另外,更灵活、更高的能效,4/3nm工艺支持,ISA指令集增强,也是Zen5的主要任务。

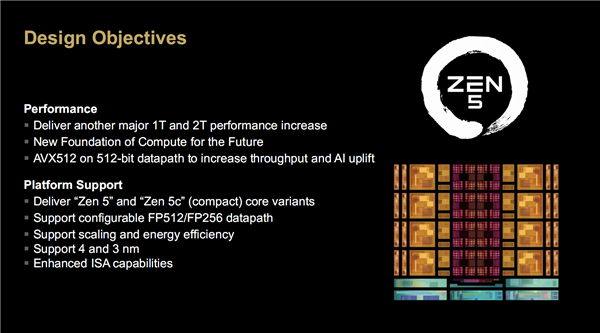

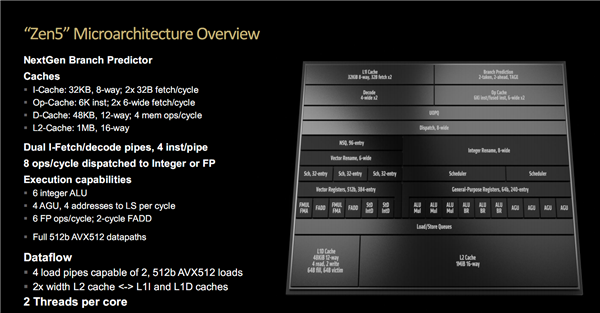

Zen5微架构总览,从前端到后端,从整数到浮点,从缓存到带宽,都进行了全面升级,后边会一一讲述。

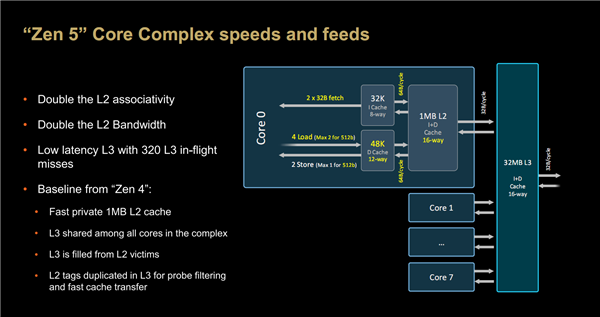

缓存部分是大家经常见到也比较容易理解的。

Zen5的一级指令缓存容量还是32KB,8路关联,每时钟周期两组32B拾取;

一级数据缓存容量增至48KB,12路关联,每时钟周期4个内存操作。

还有个特殊的操作缓存(Op-Cache),支持6个指令,每时钟周期支持两组6个宽度的拾取。

二级缓存容量还是1MB,16路关联。

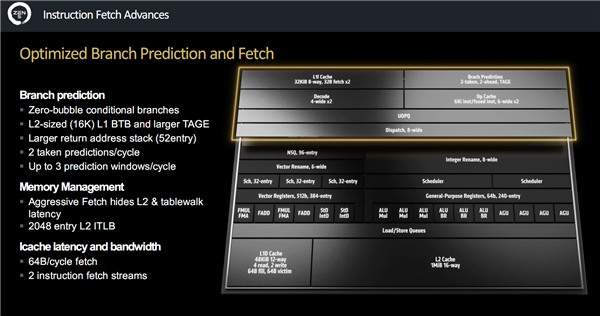

分支预测与拾取部分做了极大的优化提升,比如支持“零泡沫”(zero-bubble)条件分支,意味着分支预测器在访问BTB(分支目标缓冲)时无需付出任何代价。

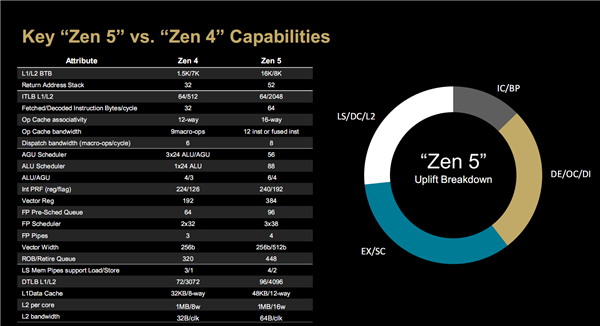

L1、L2 BTB也提升了容量(1.5K/7K来到16K/8K)和精度,并增大了TAGE,这对有条件的间接分支都很关键。

另外,每时钟周期拾取和解码指令数从32B翻番到64B,返回寻址堆栈从32个变为52个,每时钟周期支持最多3个预测窗口,指令缓存的延迟和带宽也都有所改善。

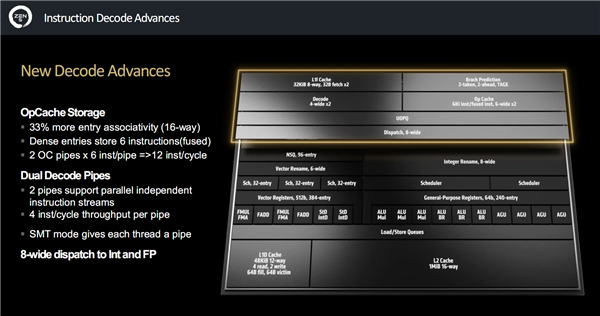

新的指令解码系统,配备了双解码流水线,可以独立并行处理指令流,每条每时钟周期4条指令。

操作缓存(OpCache)关联路数增加1/3达到了16路,可存储最多6条指令,配合双流水线,每时钟周期就是12条指令。

在开启SMT多线程的时候,每个线程都是一条流水线。

另外还很关键的是,通往整数和浮点单元的分派队列宽度从6个增至8个宏操作(macro-op),并支持操作融合,可以让来自某些指令的两个宏操作作为一个来处理。

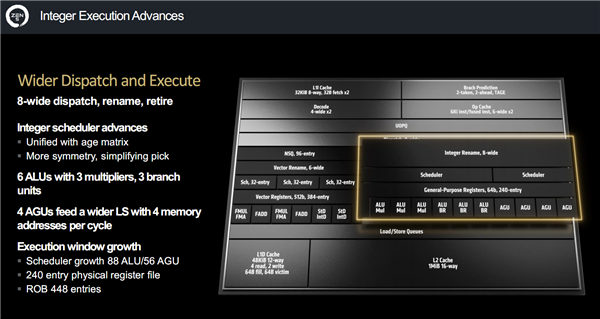

整数单元本就是Zen架构的强项,现在更加“膨胀”,分派、重命名、引退达到了8个宽度。

ALU整数逻辑单元从4个增至6个,包括3个乘法单元和3个分支单元,ALU调度器也从24个大幅增至88个。

AGU地址生成单元从3个增至4个,每时钟周期可执行4次内存寻址,AGU调度器从48个独立、24个与ALU共享变为独立的56个。

可以说,整数单元的大大强化,是锐龙9000系列在加速频率微增或不动、基准频率降低情况下取得性能大幅提升的关键所在。

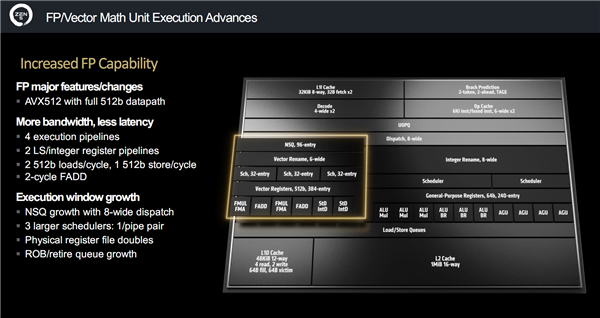

矢量和浮点能力也显著增强,尤其是AVX-512指令集终于可以支持完整的512位数据路径,同时保留256位,非常灵活,可以兼顾高性能、高效率,也不至于让功耗失控。

整个浮点执行单元的带宽和延迟都做了升级,包括4条浮点执行流水线(Zen4 3条)、3×38个浮点调度器(Zen4 2×32个)、2条载入存储与整数寄存器流水线、每时钟周期2个512位载入和1个512位存储、双循环FADD,等等。

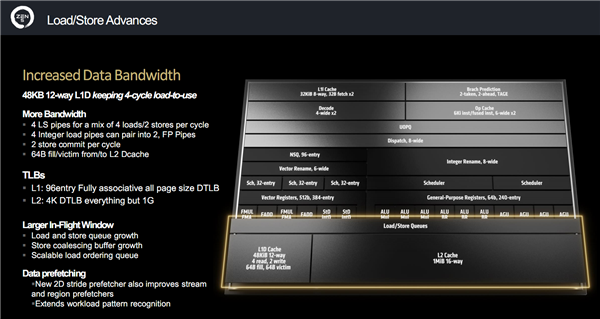

一二级缓存部分的数据带宽全面扩充,尤其是一级数据缓存来到了12路48KB,4条载入/存储流水线每时钟周期可以执行4个载入(Zen4还是3个)和2个存储,4条整数载入流水线可以合并为2条。

外还全面涉及TLB、实时窗口、数据预取等等部分。

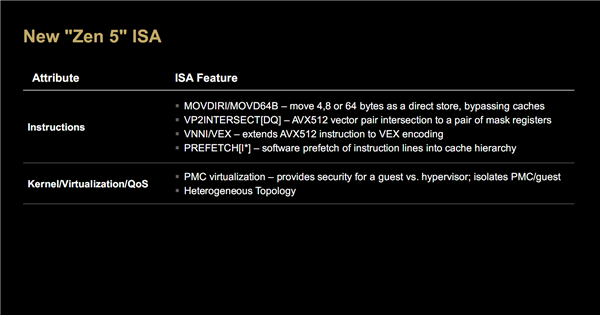

指令新增加的不算很多,AVX-512仍是重点,包括拓展至VEX编码的VNNI/VEX、矢量配对为一对掩码寄存器的VP2INTERSECT[DQ]。

另外就是Pmc虚拟化,可为客户机提供更好的安全保障,以及异构拓扑,显然是为Zen5、Zen5c的组合准备的。

Zen5、Zen4技术规格细节对比,也是对上边所讲的一个概括。

注意所有列出的参数都变了,从前端到执行单元到缓存,因此可以说Zen5是一次全面性的架构翻新,即所谓的“大改”,这才有了频率下来了但性能上去了的神奇结果。

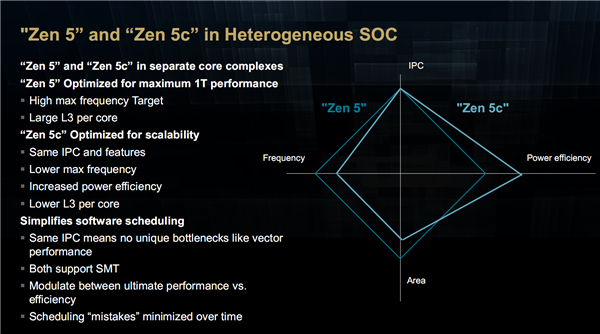

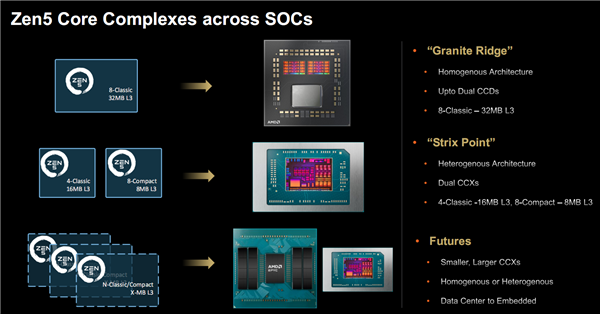

Zen5、Zen5c二者架构设计、IPC性能、ISA指令集都是完全相同的,也都支持多线程,对于操作系统和应用软件而言是透明和等价的,基本上不需要特别考虑调度问题,这和Intel的异构大小核天然不同。

Zen5的追求是尽可能高的单核频率与单核性能,还有足够大的三级缓存。

Zen5c则降低了频率,提高了能效,同时精简了部分三级缓存。

Zen5 CCX模块的核心与缓存体系结构图。

一级指令缓存基本没变,还是32KB容量,8路关联。

一级数据缓存容量增大一半来到48KB,12路关联也增多了一半,并且带宽翻番,与CPU核心之间每时钟周期支持4个载入与2个存储。

二级缓存容量还是每核心1MB,但是关联路数翻了一番达到16路,带宽也翻了一番,与一级缓存之间是每时钟周期翻番到64B,与三级缓存之间是每时钟周期32B,双向都是如此。

三级缓存每CCX 16MB,16路关联,但是降低了延迟,提高了命中率。

Zen5架构在桌面台式机、移动笔记本、服务器数据中心三大领域采取了不同的产品设计和试实现方式,都非常有针对性。

桌面上,经典chIPlet设计,一个或两个CCD(等同于CCX),外加完全延续上代设计的IOD,架构上是纯粹的Zen5,不会用Zen5c。

笔记本上,继续单芯片,双CCX组合成一个CCD。全部是Zen5、Zen5c的组合,最多分别4个、8个。

服务器上(包括嵌入式),设计更加灵活,CCX有的更大有的更小,Zen5、Zen5c都会有,但应该会和Zen4、Zen4c一样发展各自的产品线,不会混合使用。

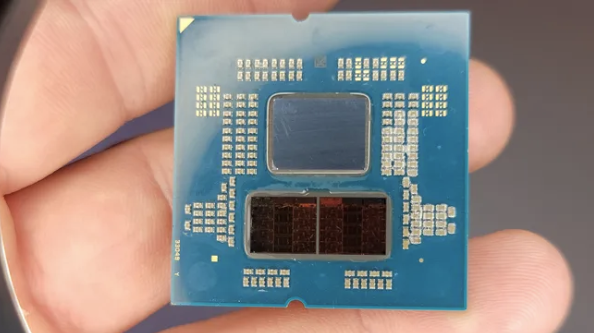

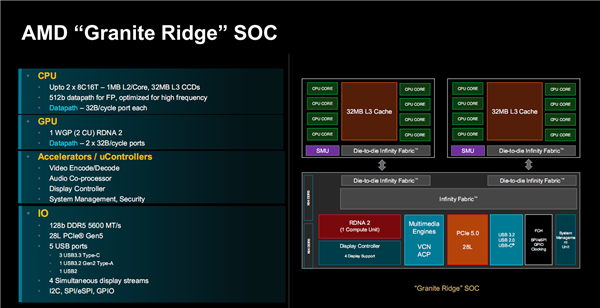

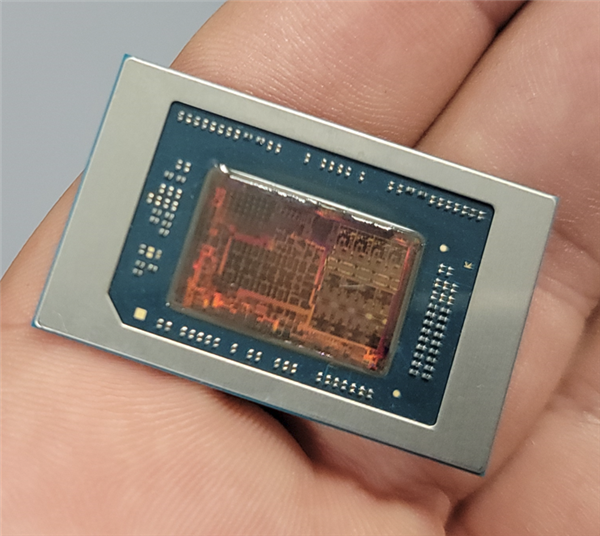

代号Granite Ridge的桌面版锐龙9000系列的裸片、核心布局图。

和之前基本一致,每一组CCX/CCD里有8个核心、8MB二级缓存、32MB三级缓存,但注意两种CCX/CCD是不互通的,所以哪怕12/16核心型号有64MB三级缓存,但每个核心最多也只能访问自己所在CCX/CCD里的32MB。

当然理论上可以通过IF总线跨越访问,但是带宽太低、延迟太高,没法用。

IOD部分和锐龙7000系列上是一样的,因此同样有2个RDNA2架构的GPU CPU单元、128位双通道DDR5-5600内存控制器、28条PCIe 5.0总线、5个USB接口、四组显示输出。

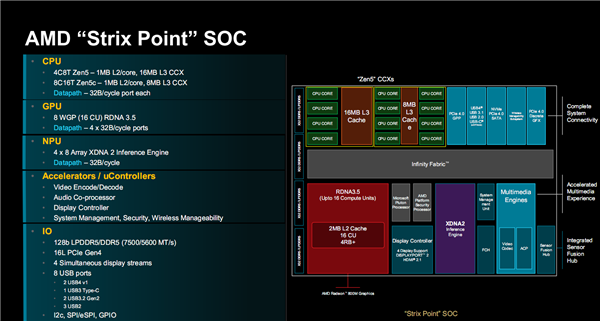

代号Strix Point的移动版锐龙AI 300系列的裸片、核心布局图。

变化还是挺大的,上一代Zen4、Zen4c组合只在两款低端型号上低调尝试,这次变成了标准的Zen5、Zen5c组合。

注意看左上角,分了两个黄色框图,4个Zen5核心和对应的16MB三级缓存是一组,8个Zen5c核心和对应的8MB是另一组,也就是和桌面上类似甚至更极端,Zen5、Zen5c三级缓存各用各的,没法互通,24MB也只是个总容量。

GPU部分是RDNA3.5架构,8组WGP也就是16个CU,1024个流处理器。NPU部分是48阵列的XDNA 2架构。这俩大家都很熟悉了。

IO部分,支持128位LPDDR5X-7500/DDR5-5600内存、16条PCIe 4.0、8个USB接口,包括两个USB4。

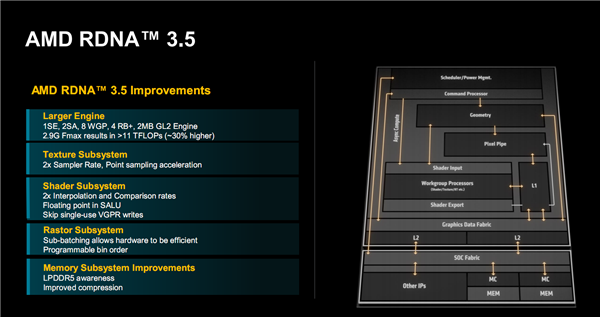

RDNA 3.5架构的GPU在纹理子系统、着色器子系统、光栅子系统、显存/内存子系统等各个方面做了优化和增强,采样率等部分指标性能翻番,可以和LPDDR5X内存更好地搭配,压缩率也更高。

当然规模也增大了,12个CU变16个CU,4个渲染后端(RB+),最高频率提升至2.9GHz,理论性能提升了大约30%,只是由于驱动还不到位,目前在游戏性能上还没释放出来。

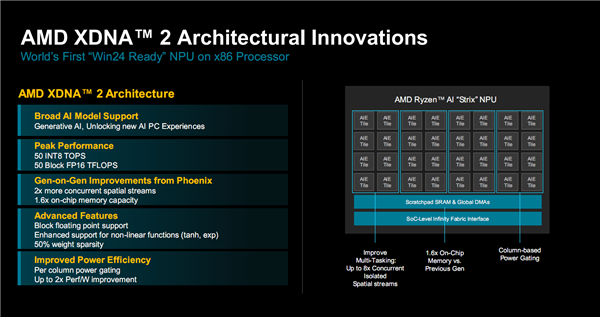

XDNA2架构的NPU AI引擎,号称第一个为“Win24”做好准备的x86处理器NPU,不过现在能用到NPU的应用还是太少了,无论AMD还是Intel。

总的来说,Zen5作为一次大规模的架构升级,从目前表现来看是相当成功的,无论笔记本上的锐龙AI 300系列,还是桌面上的锐龙9000系列,性能、能效都提升巨大、可圈可点,服务器上的第五代EPYC同样值得期待。

Intel方面即将拿出对位的Arrow Lake,错失一代之后终于回归高性能之争,又一场好戏开始了!

原文地址:news.mydrivers.com/1/996/996307.htm